# Getting Ready for WCCA

- WCCA Timelines and Scheduling

- Pre-WCCA Review

- The WCCA Plan

- Data Needs

- WCCA Process

- Challenges and Cost/Schedule Drivers

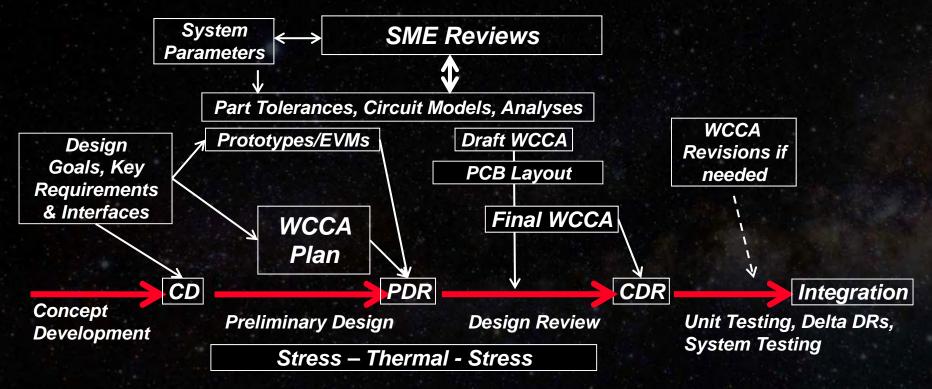

# WCCA Timelines and Scheduling

- Best Case SDRL Timing as per TOR/General experience shown above

- Its important not to forget about Stress/Thermal analysis which may need to lead the WCCA effort; much of the underlying math/models are used in both efforts so its important not to duplicate effort

- Schedule compression is VERY BAD for WCCA

- Increases Escapes, leaves shorter time to fix/reanalyze findings

- WCCA needs to be performed well before CDR but concurrent with engineering hardware/test data

#### Pre-WCCA Review

- "If there is one activity that is the most valuable it is the AEi Systems 'Pre-WCCA Review'"

- Dave E., Ball Aerospace

- Activities

- Review the design with a 'worst case eye'

- Approx. 20-40 hours per 'board'

- Expert review of the design, BOM, test procedures, Specs, etc.

- Results in a list of likely Findings which (hopefully) are addressed before the WCCA starts

- Includes Development of the WCCA Plan

- · Analysis List, Test Data Needs, SPICE Model Needs, Tolerances Needed

### The WCCA Plan

- Defining Scope What analyses are we doing and to what extent are we doing them?

- The Analysis Flow and Methodology is Key to Efficiency

- There is a sequence some analyses require inputs from others

- The list of analyses performed flows from several places

- Specifications, What is/isn't being tested, Derived Requirements, FMECA

- Need to define the Analyses, the Analysis Methods that will be used, and the Models, Tolerances Test Data, & Engineering Resources needed

- The analyses should show traceability back up to specifications

- Focus Concerns Pare Down List if (budget) necessary

- Intelligent Rigorousness is the Goal

#### Data Needs

- In order for the analysis to proceed efficiently we need to have

- Tolerance Database

- This is the heart of the analysis. Approval from all levels (customer, etc.) must occur mostly BEFORE and partially during the analysis. Any changes to tolerances will break some or all of the analysis

- Models

- Must have sufficient 'fidelity' (vendor models are usually insufficient)

- Test Data

- To fill in the data sheet holes and verify/correlate circuit models

- These needs are driven by the analyses in the Plan

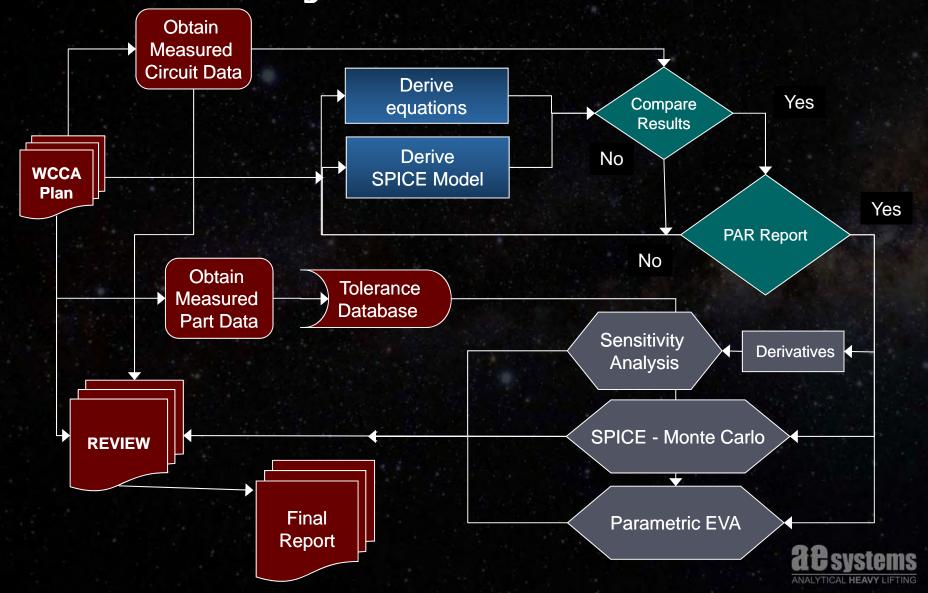

#### **WCCA Process**

Whomever is performing the WCCA must do the following:

- Review Circuit, Specifications, Requirements, and Guidelines

- Confirm List of Analyses and Compliance Criteria

- Confirm Operating Conditions range/goals for each analysis

- Obtain Tolerance Data, Construct Database

- Create Models Correlate Iterate

- Obtain Measured Data

- Perform Analysis via Sensitivity, EVA, or Monte Carlo

- Document the Analysis

- Participate in the Review

- Mitigate Findings, Propose Solution, Rework Analysis

# The AEi Systems WCCA Process

### How WCCA Saves Money

| Reasons to Perform Worst Case Analysis |                                                                                                                                                                                                    |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Need                                   | Reason                                                                                                                                                                                             |

| _                                      | To verify circuit operation and quantify the operating margins over part tolerances and operating conditions - Will the circuit perform its functions and meet specifications/To quantify the risk |

|                                        | To improve performance - to determine the sensitivity of components to certain characteristics or tolerances in order to better optimize/understand a design and what drives performance           |

|                                        | To verify that a circuit interfaces with another design properly                                                                                                                                   |

|                                        | To determine the <b>WC impact of part failures</b> or out of tolerance modes                                                                                                                       |

|                                        | To evaluate performance aspects that are difficult, expensive or impossible to measure (i.e. determine the impact of input stimulus and output loading so as not to damage hardware)               |

|                                        | To set ATP limits                                                                                                                                                                                  |

|                                        | To verify SATs/SITs and if they are needed/what their limits should be                                                                                                                             |

|                                        | To <b>reduce</b> the amount and scope of <b>testing</b>                                                                                                                                            |

|                                        | To determine if a part is suitable (too cheap, too expensive, right characteristics) or if a New                                                                                                   |

| Parts Assessment                       | Technology can be used                                                                                                                                                                             |

|                                        | To support/set critical parameters and SCD requirements/screening definition                                                                                                                       |

|                                        | To perform Single Event Transient (SET) analyses                                                                                                                                                   |

| Schedule, Cost, or                     |                                                                                                                                                                                                    |

| <b>Contractual Risk Reduction</b>      | To <b>reduce board spins</b> - determine the impact of late stage design or part changes                                                                                                           |

|                                        | To verify changes to heritage circuits                                                                                                                                                             |

|                                        | To obtain better insurance rates or reduce contractual liabilities                                                                                                                                 |

|                                        | To avoid a catastrophic or costly incident                                                                                                                                                         |

It is important to keep in mind all of the ways in which WCCA saves money and take advantage of them

## Analysis Challenges

- Poor or non-existent Part, Circuit, and System Test Data

- Labs are severely under equipped

- Hardware and WCCA time frames don't coincide

- Tolerances for key parameters missing

- WCCA requires educated assumptions We don't know a lot about the performance bounds of the parts we use

- SPICE simulation has many pitfalls

- Model development & correlation can take a long time to achieve

- Can you even tolerance the model you have?

- Signal/Power Integrity Needs but doesn't get 100% checkout Perceived low risk items get skipped

- Software expensive

- Poorly defined analysis objectives and compliance criteria Limited Specs

- Schedule is never friendly

- Is there even time to fix the things we find?

#### WCCA Cost/Schedule Drivers

- Part Variability/Radiation Data

- Validated SPICE Models

- Software Tools or Lack Thereof

- Circuit Complexity

- Qualified Personnel

- Interactive Management and Reporting

- Excessive Documentation Requirements

- Analysis "Depth" (review driven), Findings, and Reviewer Questions, Reanalysis Work

# Voltage Regulator Analysis

- Worst Case Analysis

- Stability

- Step Load

- Current Limit

- Short Circuit

- Startup/Brownout

- Conducted Susceptibility/Ripple Rejection

- Headroom

- Voltage Regulation

- Stress & Derating Analysis

- Nominal

- Worst Case

- Transient

- TOR, 1547, EEE-Inst-002 Compliant

## Switching Power Supply Analysis

#### Worst Case

- Stability

- Conducted Susceptibility CS01

- Input Conducted Emissions CE03

- UVLO

- Output Ripple

- Switching Frequency

- Efficiency

- Voltage Regulation

- Output Over Voltage Failure / Protection

- Transient Load Step Response

- Gate Drive Analysis

- Magnetics Characteristics

- Filter Analysis Damping, Impedance, Q, and Stability

#### Worst Case

- Primary Over-current Trip Threshold

- Short- Circuit

- Isolation Resistance and Capacitance

- Buss Off State Leakage Current

- Buss Transients CS06

- Inrush & Outrush

- Turn on Overshoot/Turn off

- minimum hFE

- Stress & Derating

- Nominal, Worst Case, Transient

- FMECA MTBF RADIATION