# 1.0 LP2953A LOW DROPOUT REGULATOR

# 1.1 Scope

The purpose of this analysis is to model the National Semiconductor LP2953A low dropout voltage regulator.

| Analysis:           | Regulator modeling       |  |  |

|---------------------|--------------------------|--|--|

| Performed by:       |                          |  |  |

| Last Rev Date:      | 5/10/2002                |  |  |

| Publication Number: | Nat'l LP2953A Data sheet |  |  |

| Revision:           | May 1999                 |  |  |

| SPICE File          | LP2953A.CIR              |  |  |

#### 1.2 Functional Description

The LP2953A is a low power low dropout voltage regulator with current limiting and undervoltage lockout. A shutdown input disables the regulator and discharges the output through an internal crowbar. If the output drops out of regulation, an externally available error flag goes low. An auxiliary comparator with one input tied to V ref is also provided.

### 1.3 Assumptions and Comments

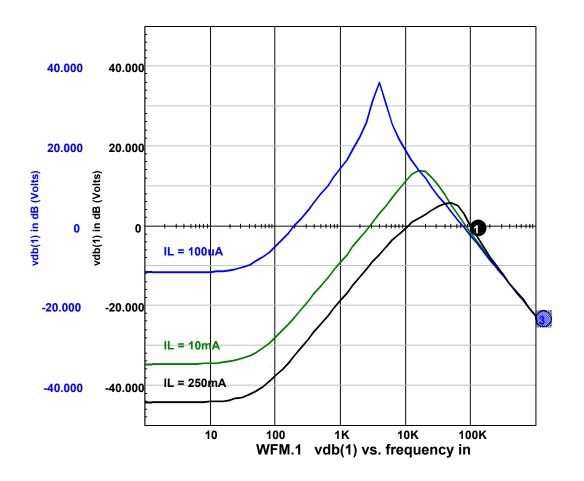

- 1. Frequency response and phase margin are modeled to agree with the customer's test data. The manufacturer's data sheet does not provide this information.

- 2. For higher frequencies, the model's frequency response does not agree with the customer's test data. The customer's data is believed to be in error. In particular, above a few hundred kHz, the gain of the regulator is actually lower than that of the test circuit's 10 ohm resistor / load capacitor, so at higher frequencies, the customer's bode plot is a plot of the test circuit, not of the regulator. This is the cause of the 180 degree phase reversal at ~400kHz. The test circuit spice model also exhibits this behavior but at a higher frequency. Note that the regulator's actual performance is more stable than the customer's data would suggest.

- 3. Gain margin is not modeled.

- 4. In order to agree with the customer's data for frequency response, output impedance could only be approximately modeled.

- 5. Current limiting is modeled, but the foldback characteristics of mfr's fig. 44 are not modeled.

- 6. Hysteresis is not modeled for any of the comparator inputs.

- 7. The inversion of the error output during shutdown ( $Vin \le 1.3V$ ) is not modeled.

- 8. Load transient response is approximately modeled.

- 9. Quiescent and ground current are approximately modeled to agree with mfr's fig. 27 and 30.

## 1.4 SPICE Simulations and Analyses

The model was simulated and the results were compared to data supplied by the customer as well as the manufacturer's data sheet. The Spice simulation results are shown below.

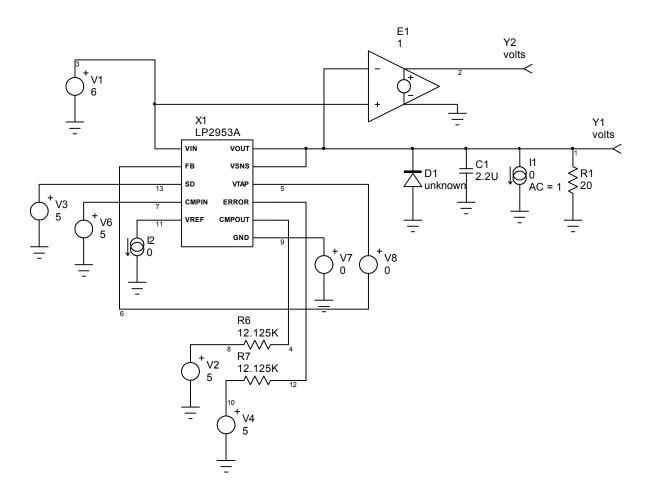

SPICE test circuit for manufacturer's test conditions

### **Output Impedance**

**SPICE** Waveforms of output impedance

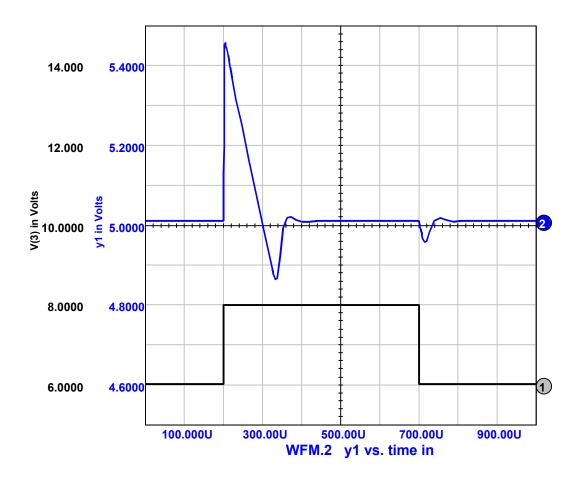

## Line transient response

SPICE Waveforms of line transient response

IL = 10mA

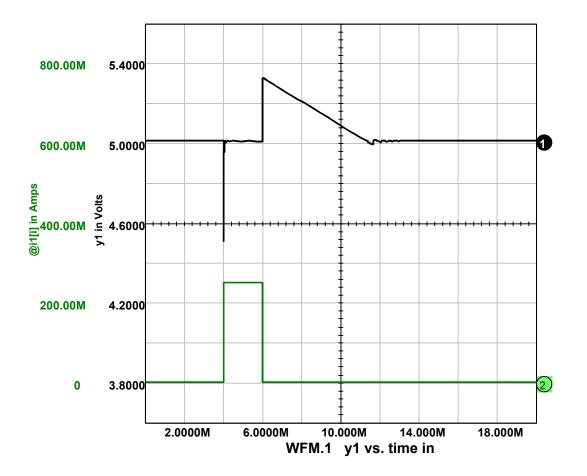

## Load transient response

SPICE Waveforms of load transient response

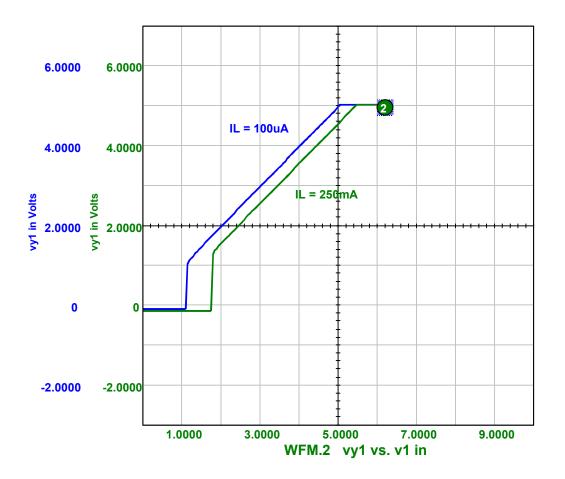

## **Dropout characteristics**

SPICE Waveforms of dropout characteristics

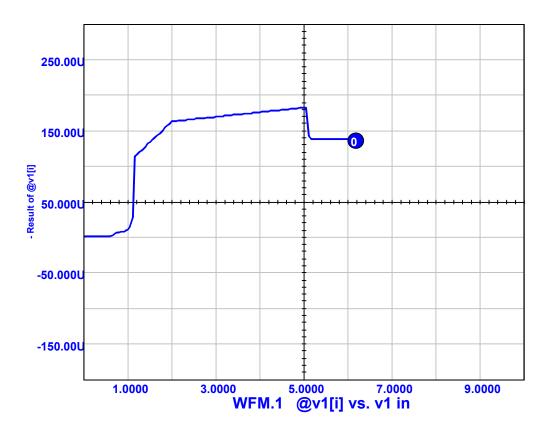

#### **Quiescent current**

SPICE Waveform of quiescent current

IL = 100uA

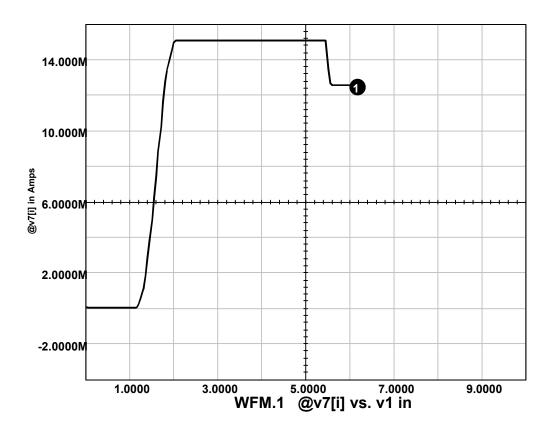

## Ground pin current

SPICE Waveform of ground pin current

### IL = 250mA (R6 and R7 deleted from test circuit)

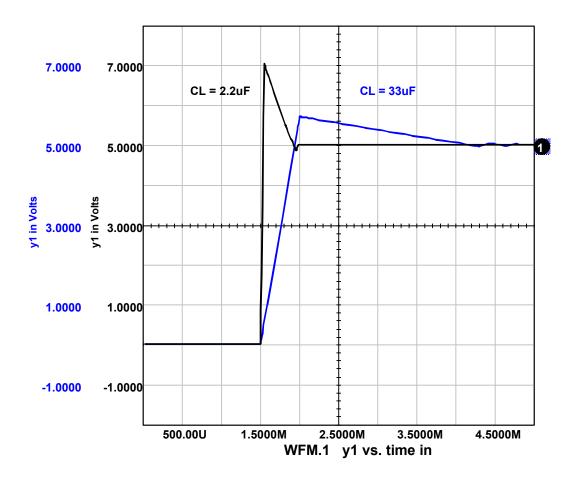

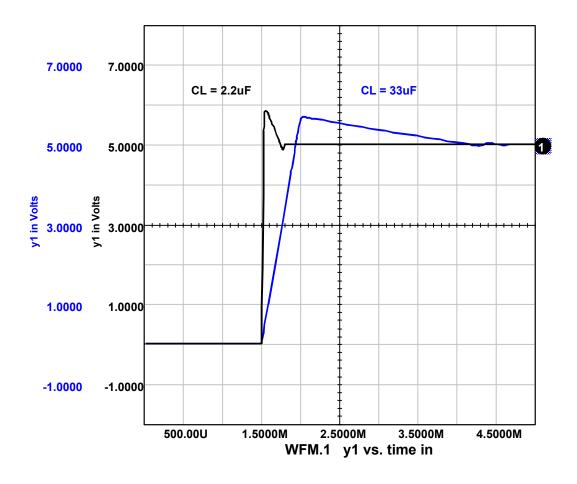

#### **Enable transient**

### SPICE Waveforms of enable transient

IL = 10mA, V IN = 14V

IL = 10mA

## 5.4.6 Conclusions and Recommendations

The Spice simulation results are summarized below in table 1 and are within the manufacturer's electrical specifications. Frequency response agrees with data supplied by the customer except as noted above.

## Table 5.4.1 LP2953A SPICE Model - Summary of Simulation Results

| Parameter                                          |                | Тур Ѕрес | SPICE UNITS   |

|----------------------------------------------------|----------------|----------|---------------|

| REGULATOR                                          |                |          |               |

| Output voltage, customer's test circuit            |                | 2.758    | 2.756 V       |

| mfr's test conditions                              |                | 5.00     | 5.01 V        |

| Output voltage load regulation, IL = 1 to 250mA    |                | 0.04     | 0.042 %       |

| IL =                                               | 0.1 to 1mA     | 0.04     | 0.002 %       |

| Output voltage line regulation, V in = 6 to 30V    |                | 0.03     | 0.03 %        |

| Phase Margin, customer's test circuit, IL = 80mA   |                | 78.56    | 78.55 degrees |

|                                                    | at             | 27.9     | 25.7 kHz      |

|                                                    | IL = 50mA      | 75.26    | 76.32 degrees |

|                                                    | at             | 22.7     | 22.5 kHz      |

|                                                    | IL = 1mA       | 42.26    | 48.64 Degrees |

|                                                    | at             | 3.8      | 4.5 kHz       |

| Dropout Voltage, IL = 1mA                          |                | 60       | 90 mV         |

| IL = 50mA                                          |                | 240      | 236 mV        |

| IL = 100mA                                         |                | 310      | 298 mV        |

| IL = 250mA                                         |                | 470      | 465 mV        |

| Current limit, R out = 1 mOhm                      |                | 380      | 384 mA        |

| Reference voltage                                  |                | 1.23     | 1.23 V        |

| Reference voltage line regulation, V in = 6 to 30V |                | 0.03     | 0.03 %        |

| V                                                  | in = 2.5 to 6V | 0.03     | 0.0044 %      |

| Reference voltage load regulation, IL = 0 to 200uA |                | 0.25     | 0.25 %        |

| Feedback pin bias current                          |                | 20       | 20 nA         |

| Output off pulldown current                        |                | 50       | 49.9 mA       |

| DROPOUT DETECTION COMPAR                           | ATOR           |          |               |

| Output "HIGH" leakage                              |                | 0.01     | 0.01 uA       |

| Output "LOW voltage                                |                | 150      | 149 mV        |

| Upper threshold voltage                            |                | 60       | 60 mV         |

| Lower threshold voltage                            |                | 85       | 60 mV         |

# Table 5.4.1 Summary of Simulation Results (cont.)

| Parameter             | Typ Spec | SPICE UNITS |

|-----------------------|----------|-------------|

| SHUTDOWN INPUT        |          |             |

| Input offset voltage  | 3        | 3 mV        |

| Input bias current    | 10       | 10 nA       |

|                       |          |             |

| AUXILIARY COMPARATOR  |          |             |

| Input offset voltage  | 3        | 3 mV        |

| Input bias current    | 10       | 10 nA       |

| Output "HIGH" leakage | 0.01     | 0.01 uA     |

| Output "LOW voltage   | 150      | 149 mV      |